Posted On: Sep 5, 2017

Since we made Amazon EC2 F1 instances generally available earlier this year, we have seen exciting adoption by customers, partners and the developer and research community. Customers are using F1 for accelerating a diverse set of applications such as genomic processing, data analytics, security, image and video processing and machine learning. F1 Partners and developers are taking advantage of AWS Marketplace to make their innovations available to the broader community of AWS customers.

Today we are excited to announce the preview of a development workflow that allows customers to use OpenCL with Amazon EC2 F1 FPGA Instances to accelerate their C/C++ applications. Software developers with little to no FPGA experience, will find a familiar development experience and now can use the cloud-scale availability of FPGAs to supercharge their applications. To sign-up for the preview, please visit the preview page.

We are also making F1 instances available in our US West (Oregon) and EU (Ireland) regions. To get started using F1 instances in these new regions, you can use the AWS Management Console, AWS Command Line Interface (CLI), or AWS SDKs.

Based on customer feedback, we have also added new features and improvements into F1 HDK Release 1.3.1, AWS FPGA Shell, FPGA Developer AMI and the SDK.

The Amazon FPGA Shell now provides dramatically better utilization of the Custom Logic (CL) area available to the developers. Simply put, this means that developers can now achieve higher FPGA area utilization, enabling larger or faster acceleration logic. We added FPGA-initiated read/write over PCI to the host CPU allowing FPGA logic to initiate data transfers to/from the host CPU applications. We also improved the UltraRAM utilization, enabling the CL to utilize all of the FPGA URAM blocks, useful for designs that need low latency memory access. We have expanded the DMA support, allowing DMA transactions of any size. We have also added support for multi-queue in each direction. For further details, click here.

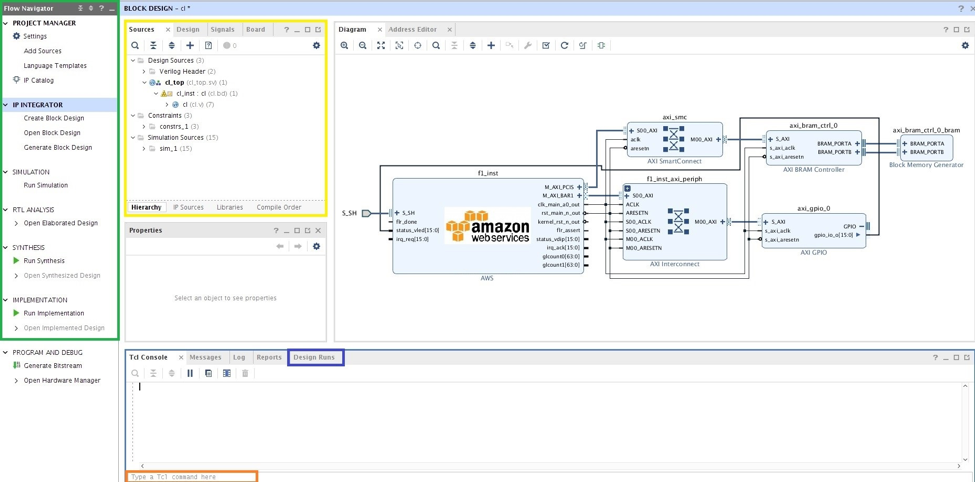

The FPGA Developer AMI now enables a graphical design canvas, enabling faster AFI development using a graphical flow, and leveraging pre-integrated verified IP blocks.

For more details, click here. We have also upgraded the FPGA Developer AMI to Vivado 2017.1 SDx, improving the synthesis quality and runtime capabilities.

On the SDK side, we have improved the API usability by supporting synchronous mode for fpga-load-local-image and fpga-clear-local-image by default; For more details, click here.

To learn more about F1 instances and FPGA Cloud development, visit our Github, and checkout the FPGA developer forum.